Analyse de grands modèles de simulation pour une répartition idéale sur un ou plusieurs FPGA à l’aide du dSPACE Electrical Power Systems Simulation Package

Lorsque vous créez des modèles de simulation complexes pour les circuits d’électronique de puissance, les modèles peuvent devenir trop grands pour être calculés sur un seul FGPA sans optimisation. La question se pose alors de savoir comment réduire l’effort de calcul et où, si nécessaire, les interfaces idéales doivent diviser le modèle en sous-systèmes significatifs. Ici, vous devez garantir que la qualité des résultats n'est pas aggravée par une séparation défavorable.

Un exemple concret sera utilisé pour illustrer une approche générique que dSPACE fournit pour cette tâche.

Analyse du modèle en termes de taille et de dépendances

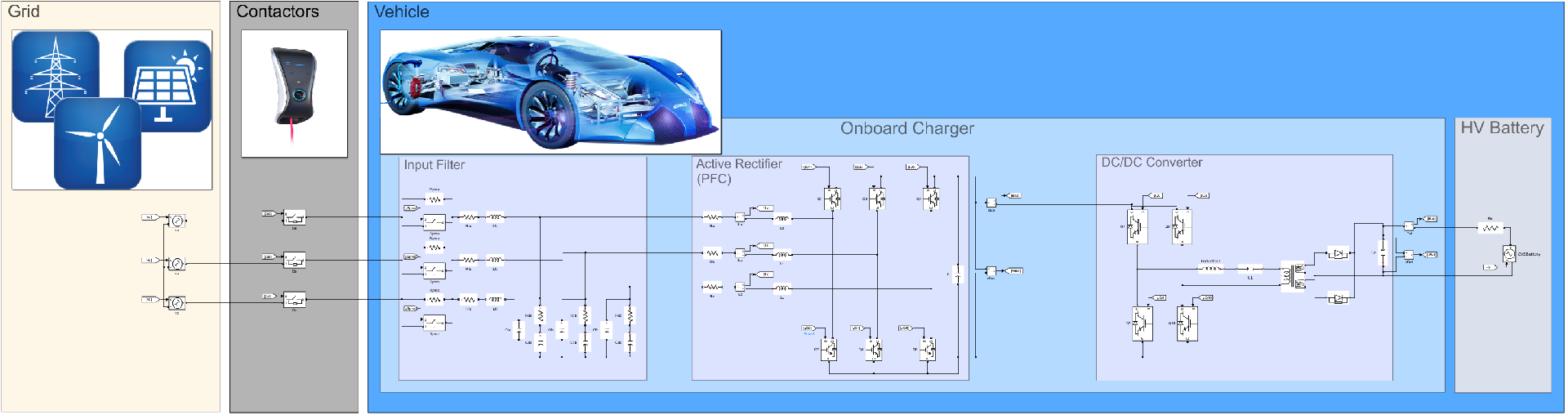

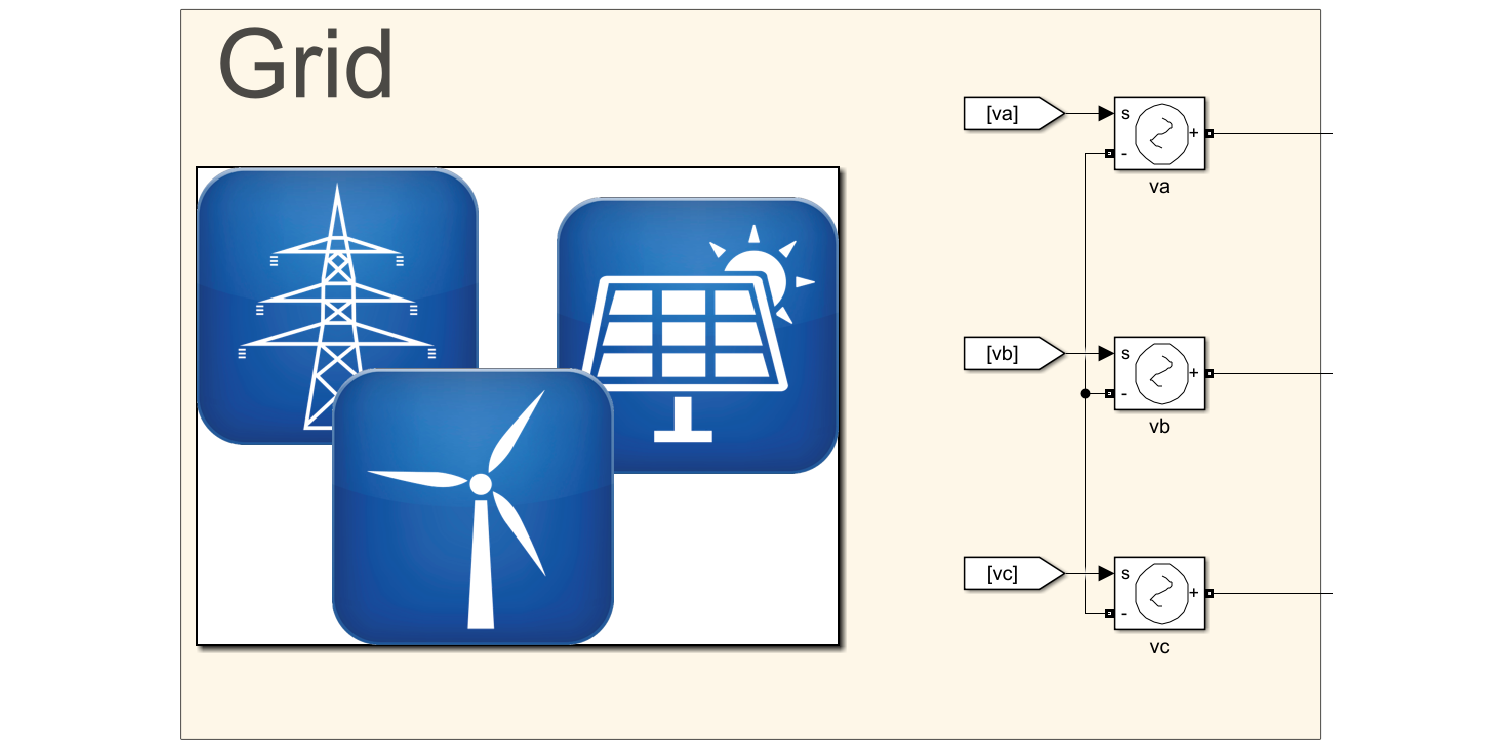

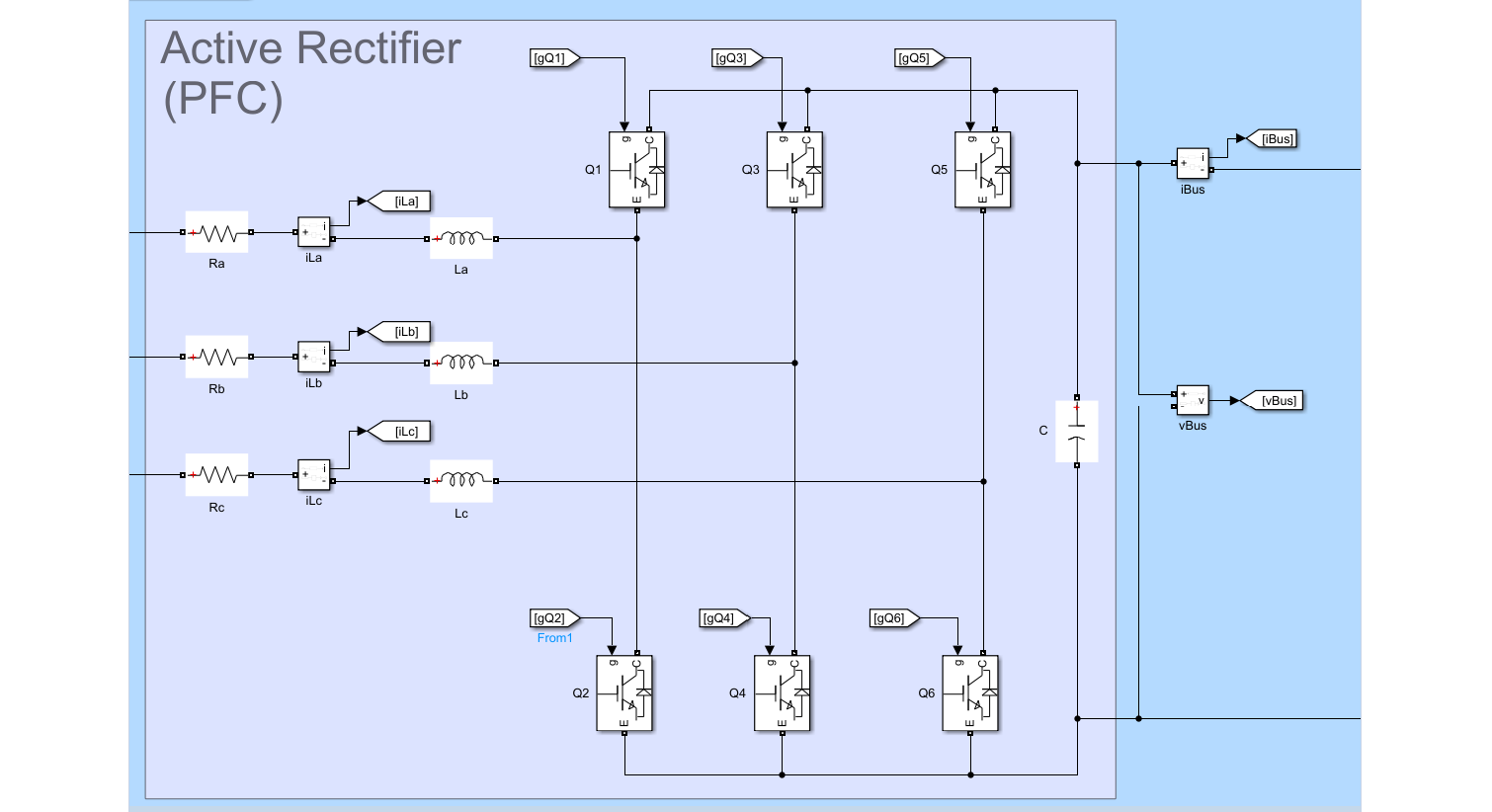

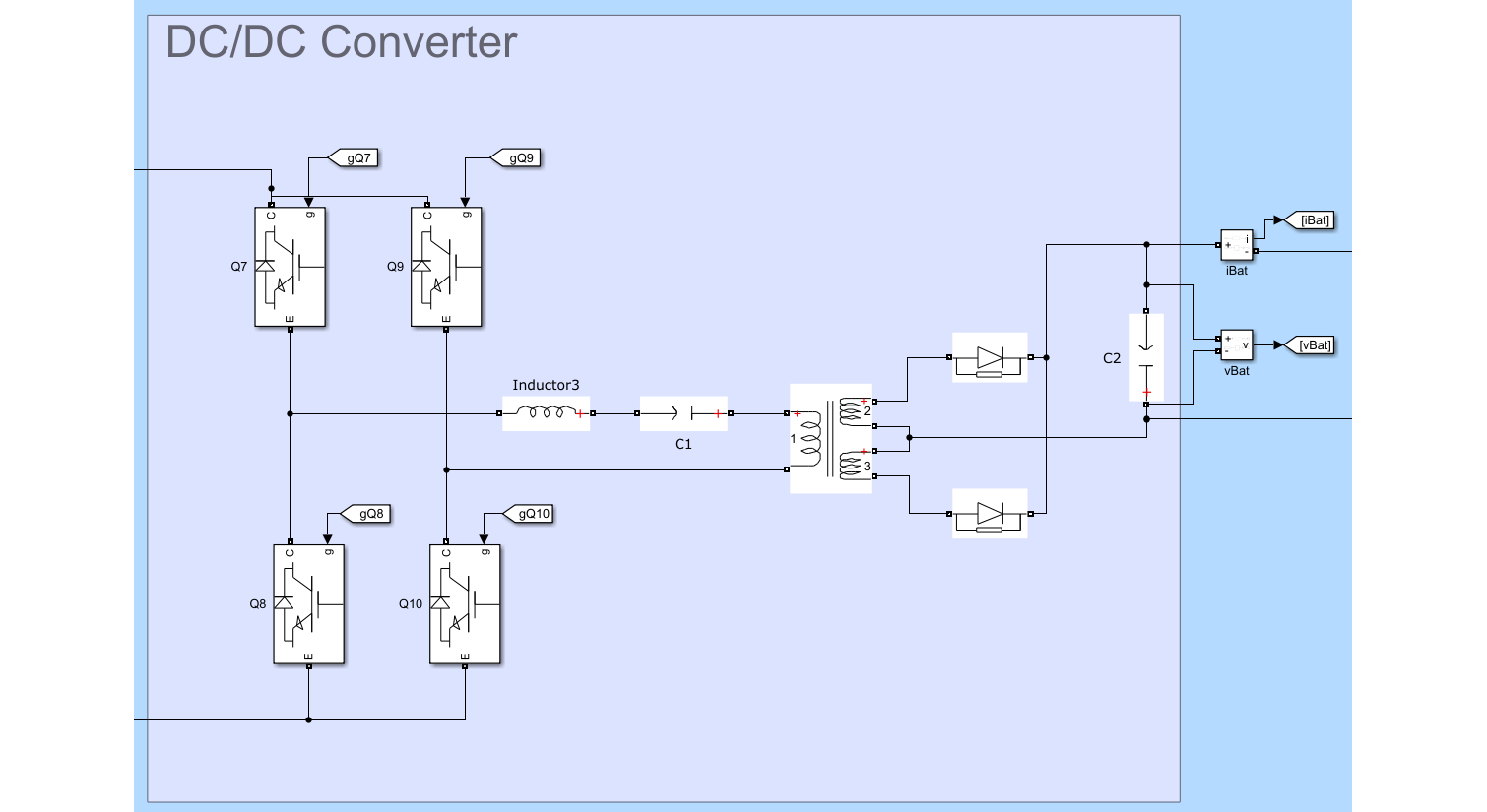

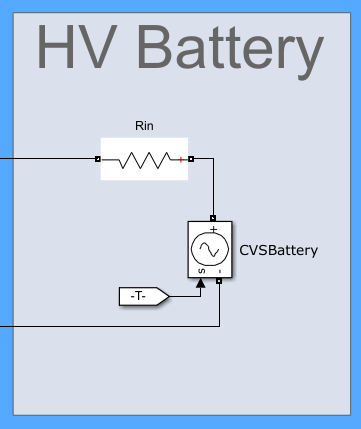

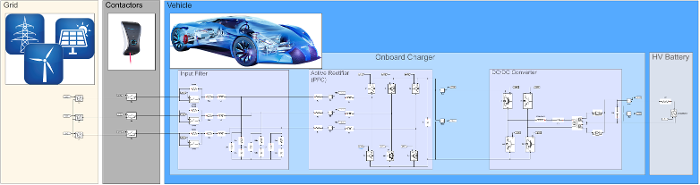

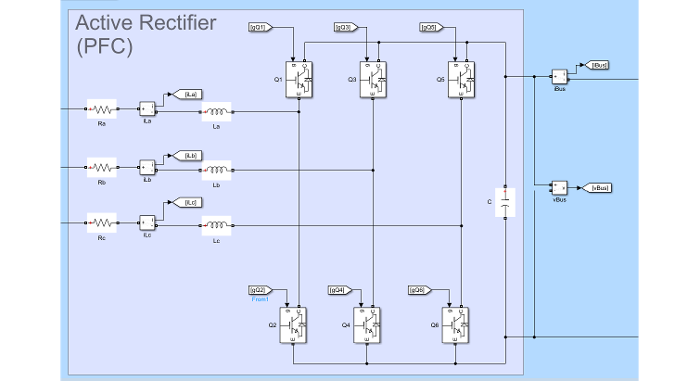

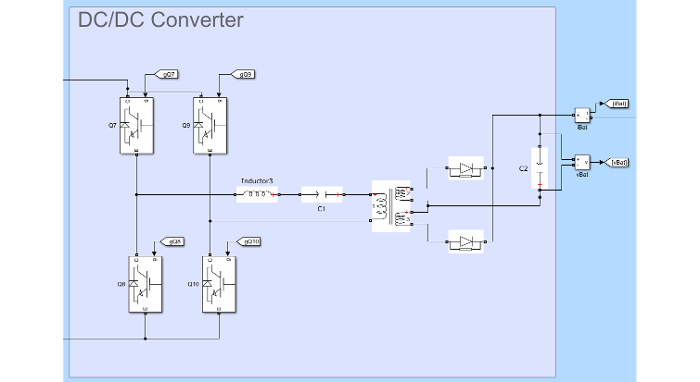

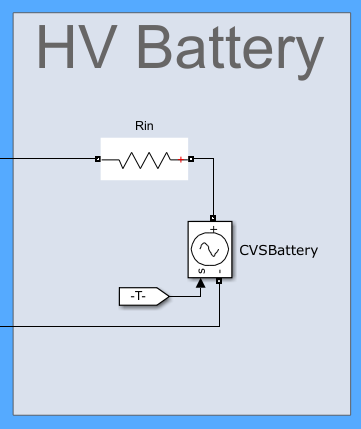

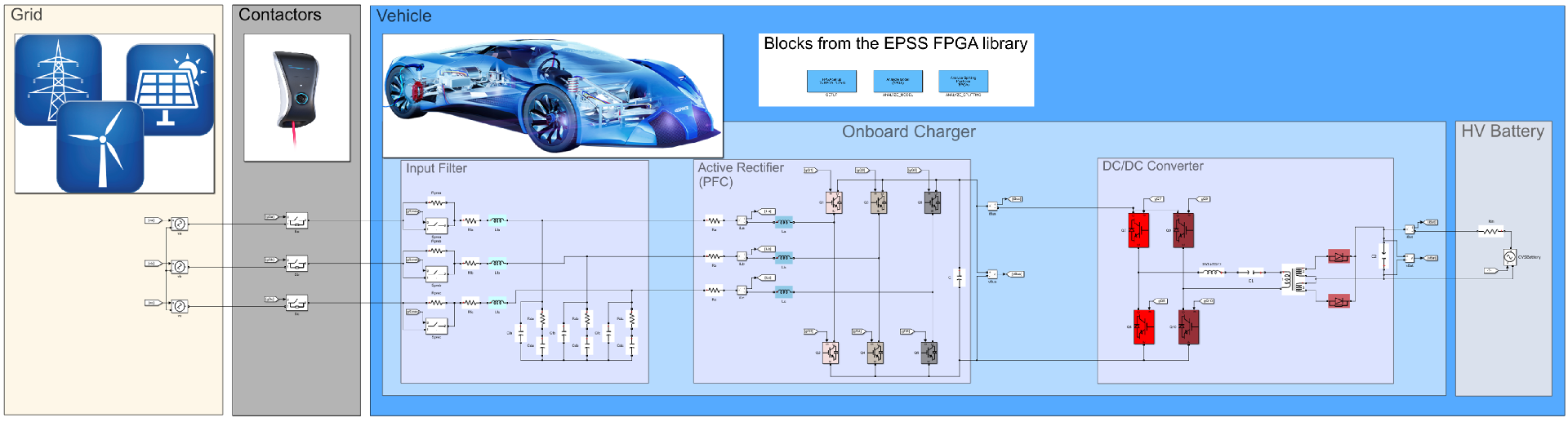

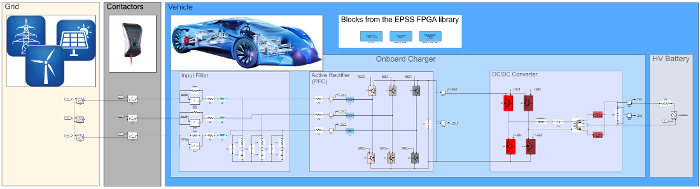

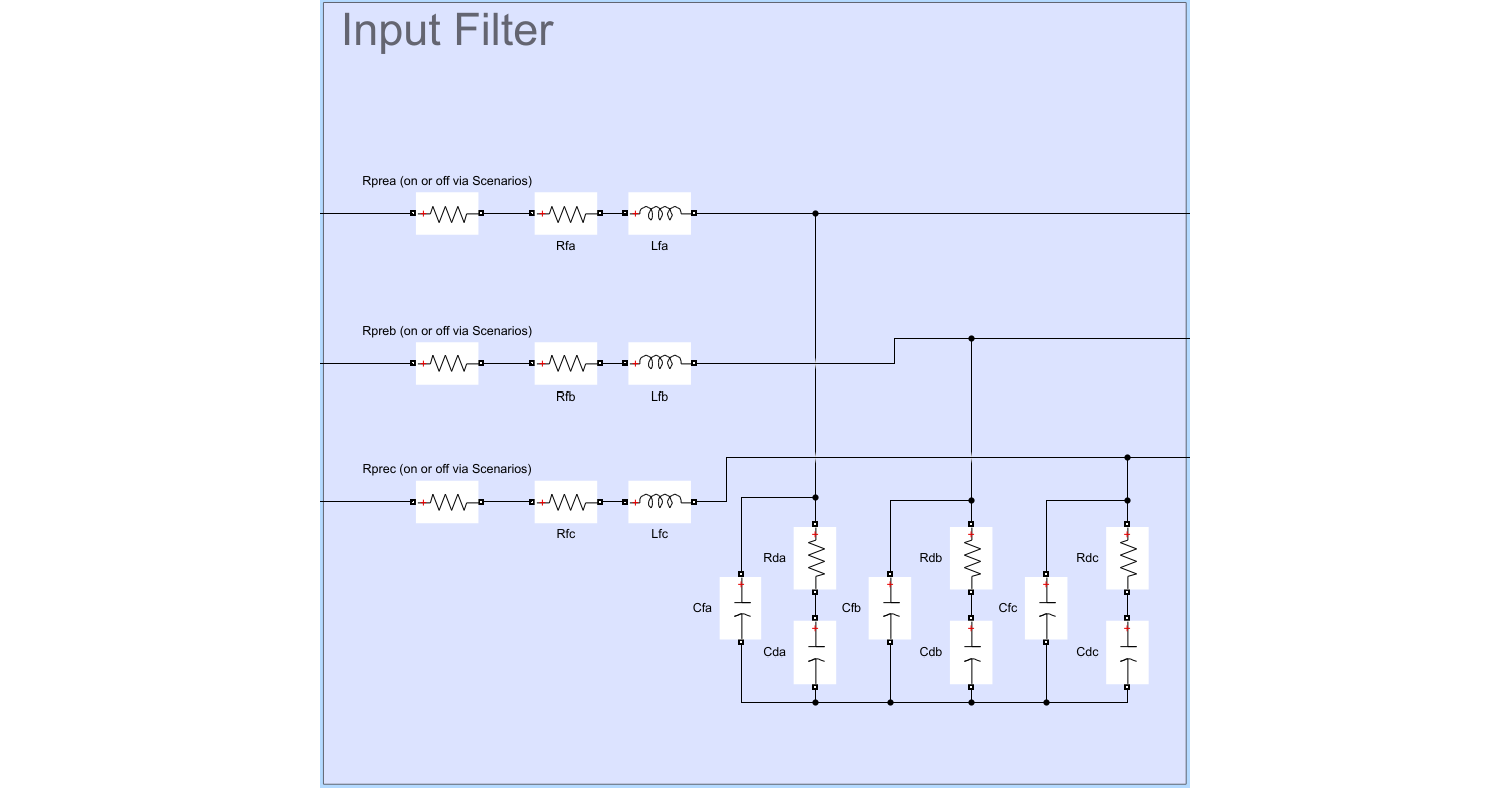

Le point de départ est le modèle d’un véhicule électrique avec un chargeur embarqué connecté au réseau électrique au moyen d’un wallbox, créé avec la boîte à outils MATLAB®/Simulink® Simscape Electrical TM (Specialized Power Systems).

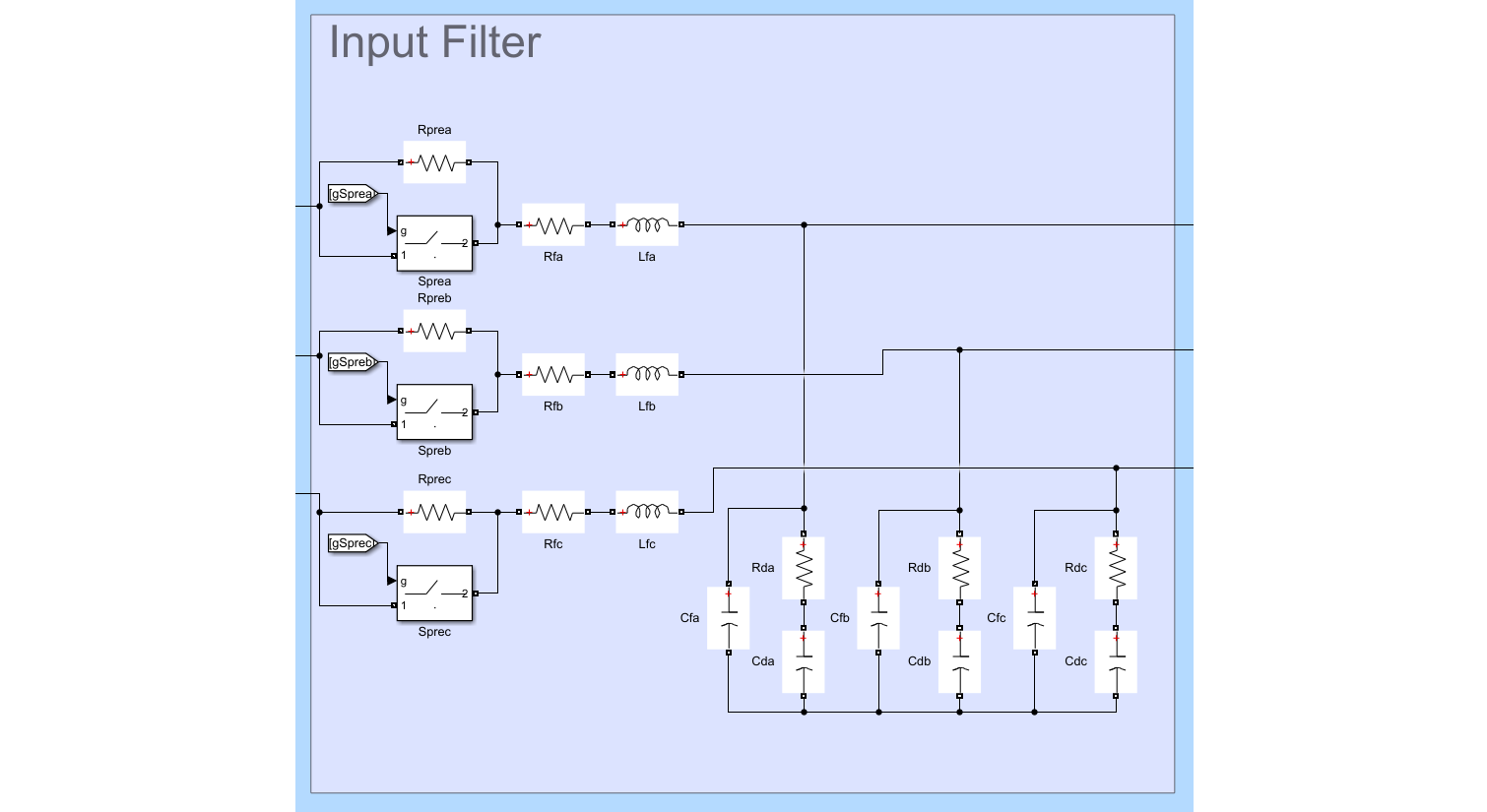

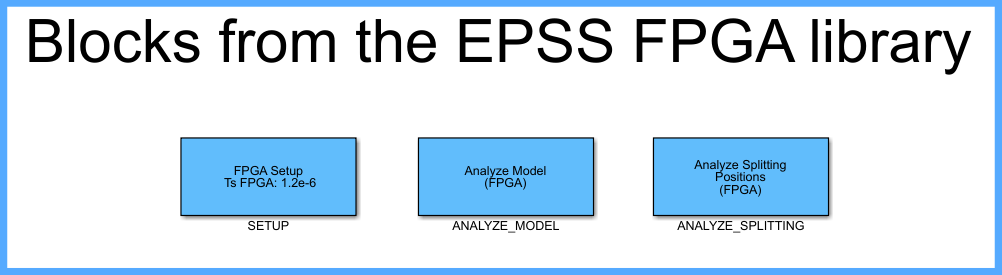

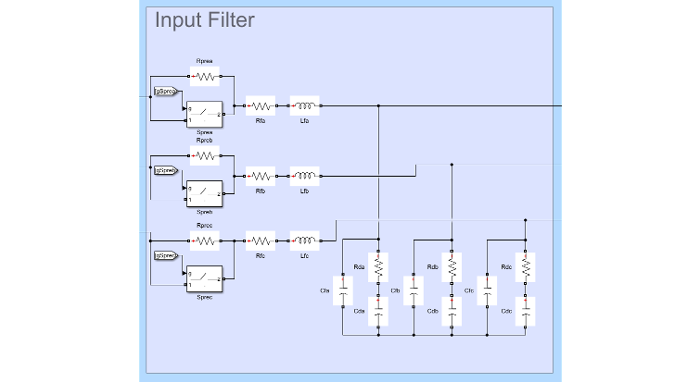

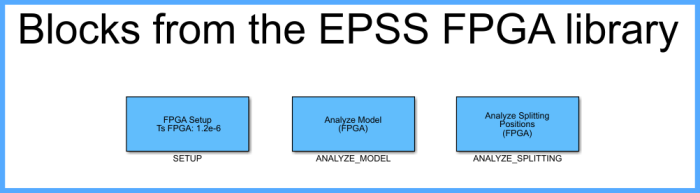

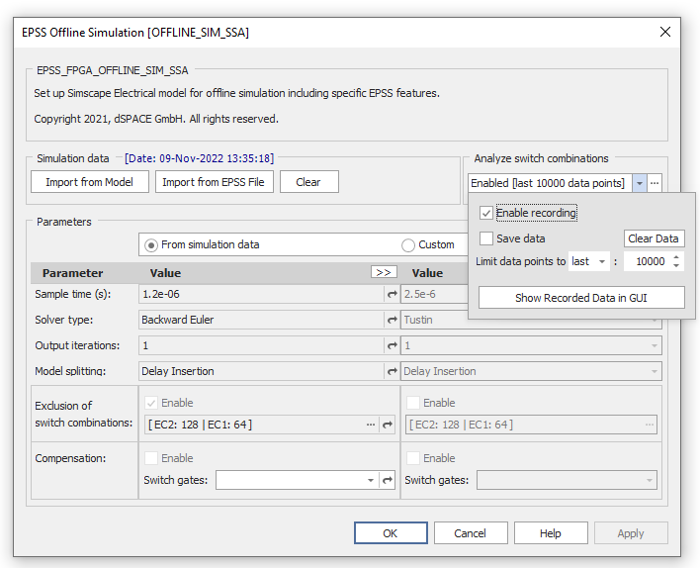

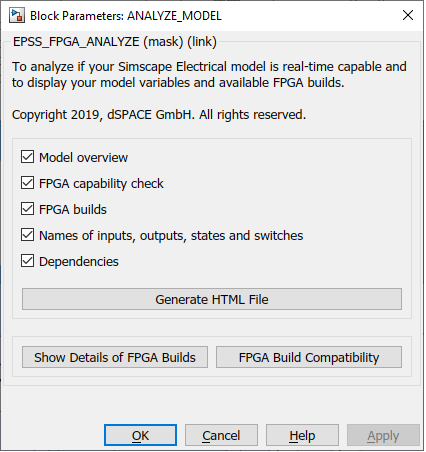

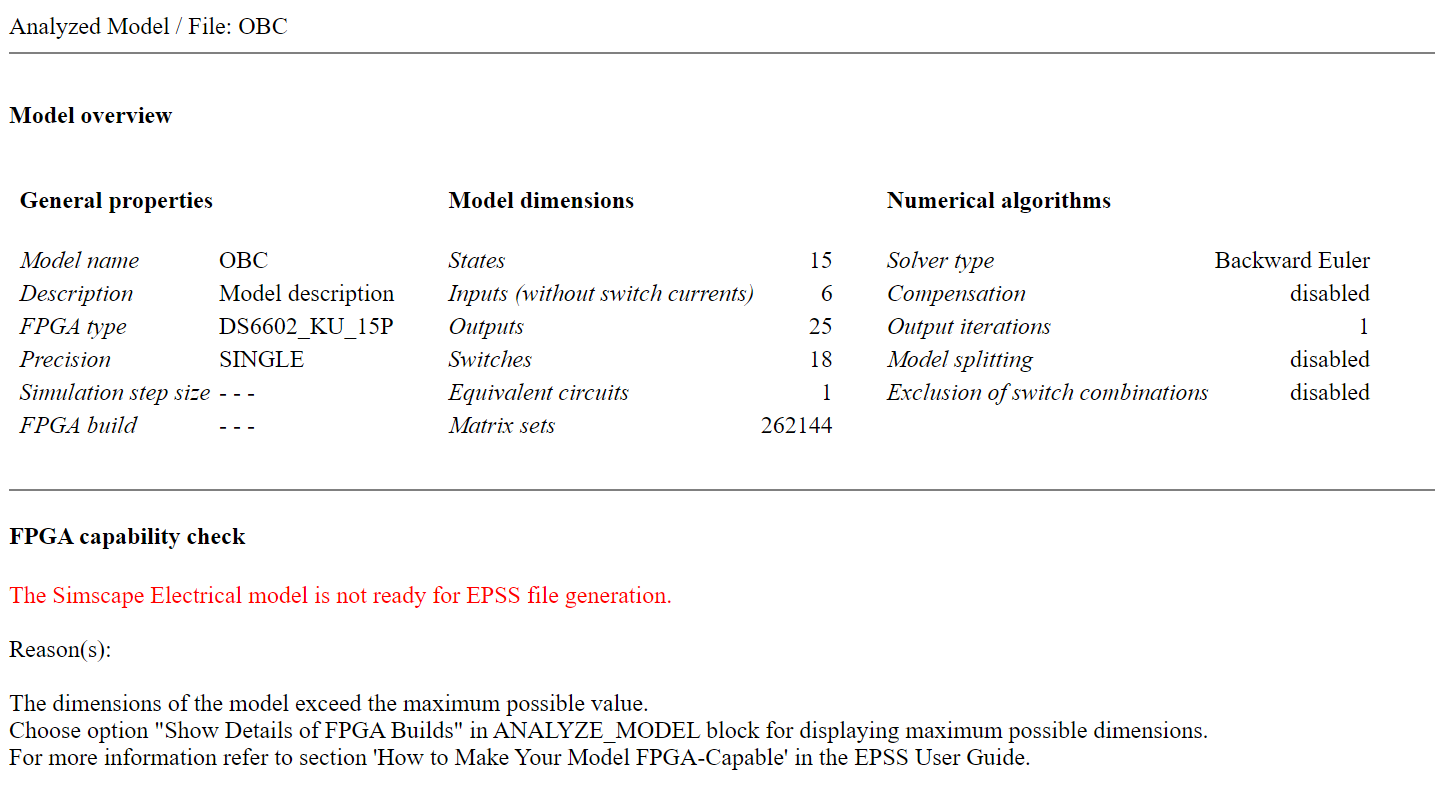

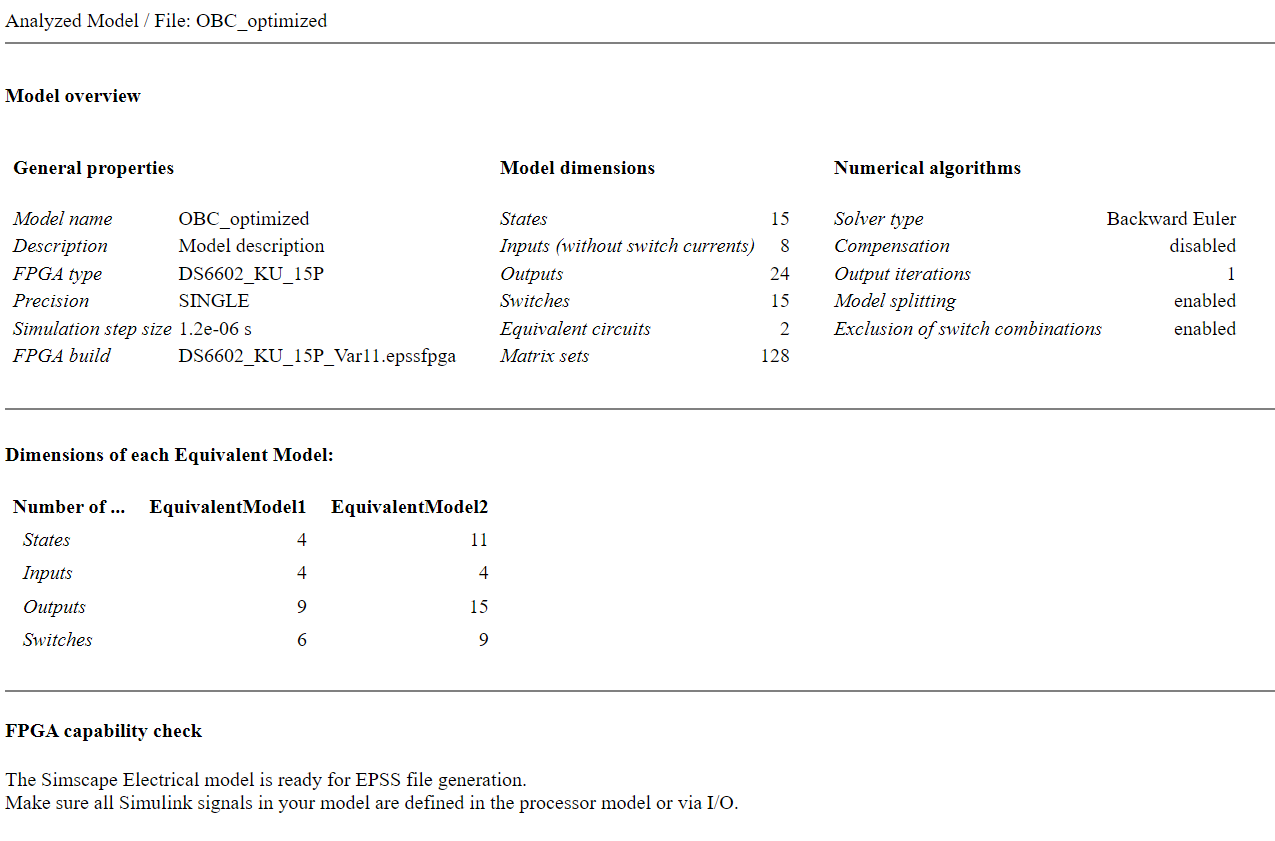

La première étape est une analyse du modèle, qui permet de déterminer si le modèle peut être calculé directement avec le FPGA disponible. À cet effet, le pack EPSS (Electrical Power Systems Simulation) de dSPACE offre une fonction d'analyse. Dans notre cas, le résultat est que le modèle avec ses 262 144 jeux de matrice, chacun composé de matrices système, d'entrée, de sortie et de passage, est trop grand pour la vitesse maximale et la mémoire disponibles sur le FPGA. Ce grand nombre de jeux de matrices résulte du fait que pour les 18 commutateurs inclus dans le modèle, en théorie, toutes les 2 18 = 262 144 configurations possibles pourraient être envisagées.

Si l’analyse avait montré que le modèle pouvait être calculé sur le FPGA dans son intégralité, un fichier EPSS aurait été généré pour le modèle, qui contient toutes les données nécessaires à la simulation en temps réel et peut être inclus dans la configuration E/S du système via le logiciel dSPACE ConfigurationDesk. Dans le cas de la topologie du chargeur embarqué illustré ci-dessus, le modèle global n’est pas adapté pour simuler les configurations complètes avec toutes les combinaisons de commutateurs possibles, le fichier EPSS n’a donc pas pu être généré.

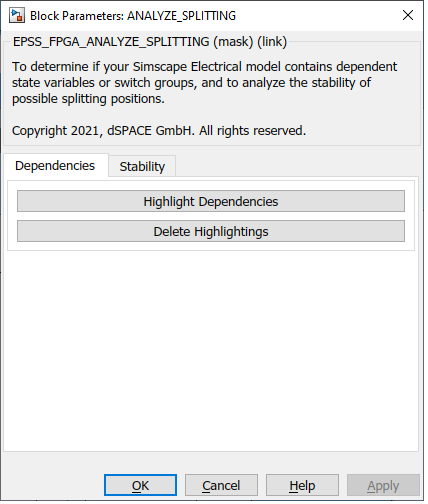

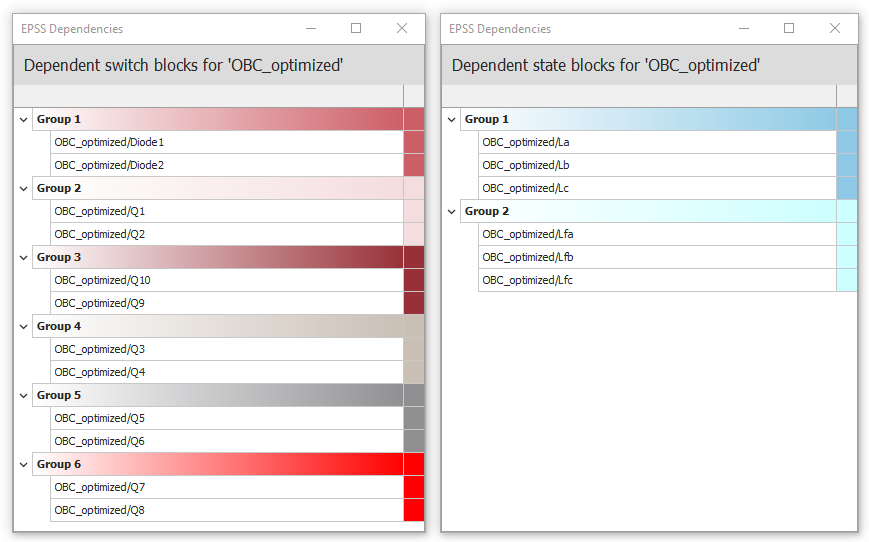

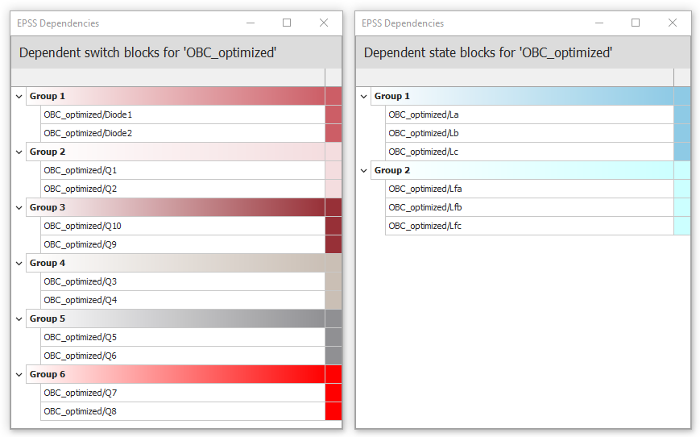

Modélisation des dépendances dans le schéma électrique

Le bloc ANALYZE_SPLITTING inclus dans EPSS fournit une représentation visuelle qui montre les composants du modèle qui sont mathématiquement solidaires et ne doivent pas être séparés. Ici, les variables d'état dépendantes, en particulier les tensions condensateurs et les courants inducteurs, et l'effet possible des événements de commutation sur d'autres éléments de commutation sont calculés. Les éléments qui sont solidaires sont chacun marqués de la même couleur et leurs dépendances sont donc représentées visuellement.

Vérification des positions de fractionnement possibles

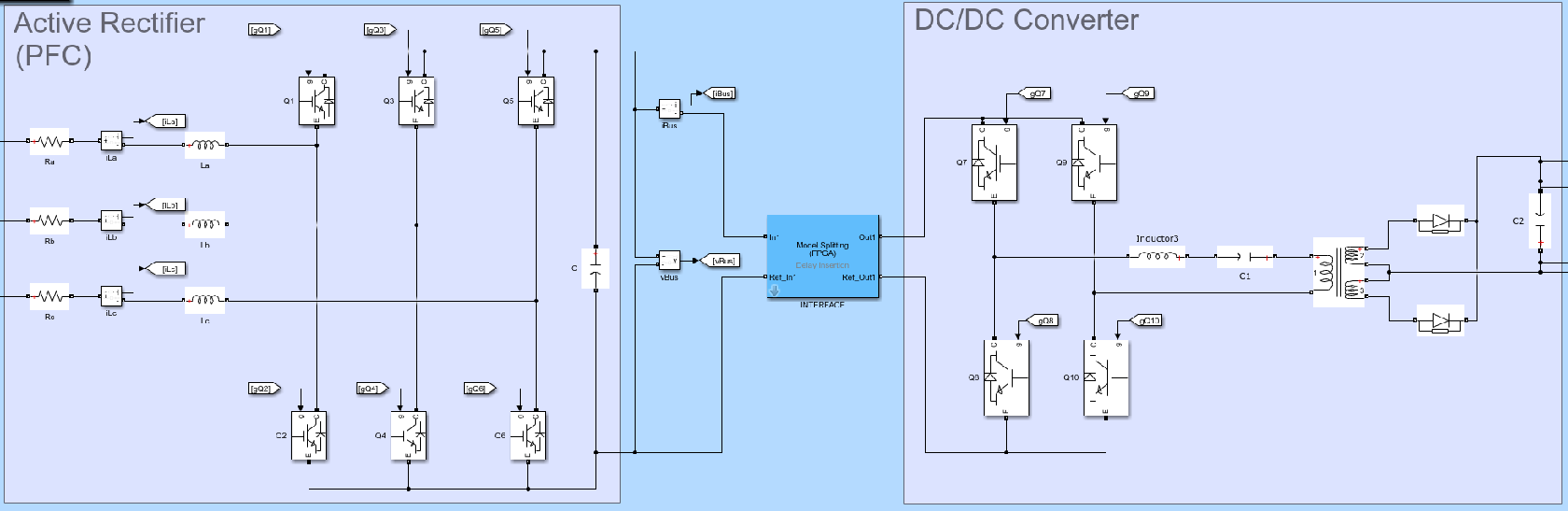

Dans le schéma de principe, des blocs de fractionnement spéciaux contenus dans EPSS (appelés blocs INTERFACE) peuvent être insérés en différents points du schéma électrique afin que les commutateurs soient répartis aussi équitablement que possible et que les groupes dépendants ne soient pas séparés. Une position de fractionnement possible est illustrée sur la figure suivante. Le bloc INTERFACE pour le fractionnement du modèle a été placé de sorte que ni les groupes de commutateurs ni les états dépendants n'ont été séparés. Une réexécution de la fonction d’analyse montre une réduction significative des jeux de matrices à stocker sur le FPGA de 262 144 à 4 096.

L’étape suivante consiste à vérifier si le système global est stable même avec le point de fractionnement sélectionné.

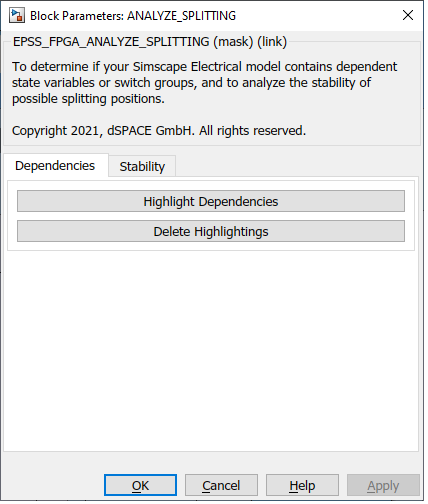

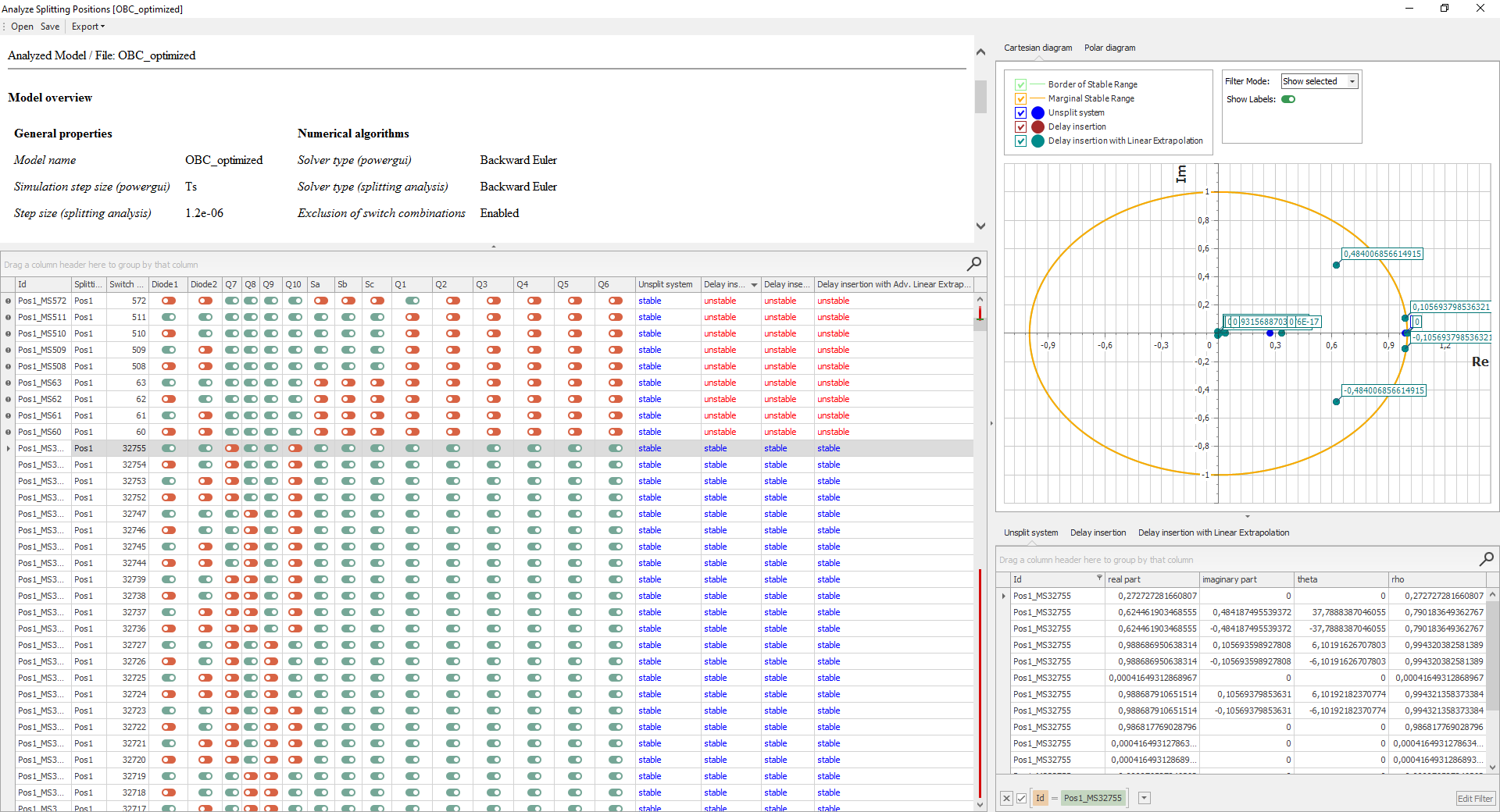

Vérification de la stabilité des positions de fractionnement possibles

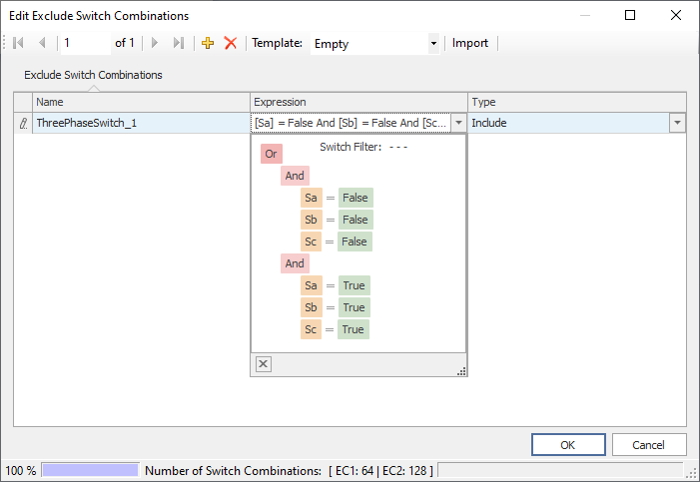

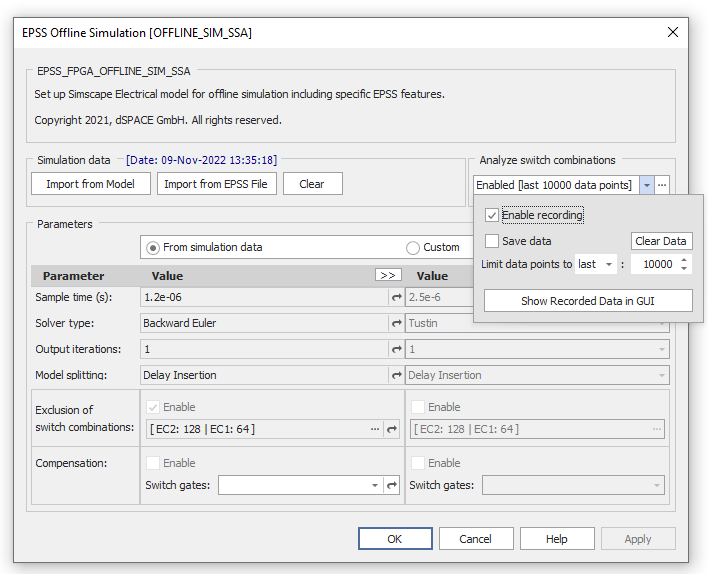

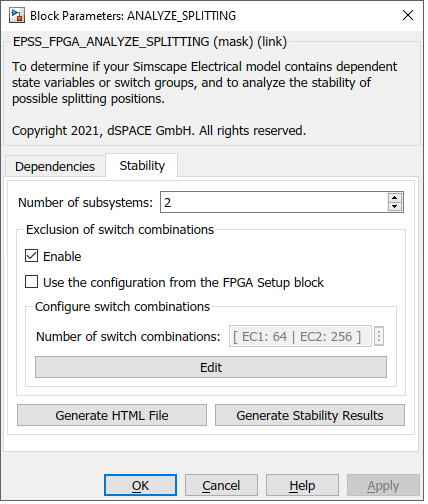

Le bloc ANALYZE_SPLITTING de l'EPSS vous permet d'évaluer facilement si la position sélectionnée du bloc INTERFACE ou un ensemble de positions possibles des blocs INTERFACE assure des propriétés stables du système pour chaque configuration de commutateur. Pour exclure les combinaisons de commutateurs non réalistes et accélérer le temps de calcul, le comportement de commutation peut être configuré via l'option « Exclusion of switch combinations ». Dans le présent exemple, les commutateurs parallèles du wallbox et du filtre peuvent chacun être configurés en tant que commutateurs triphasés, car ils commutent toujours simultanément.

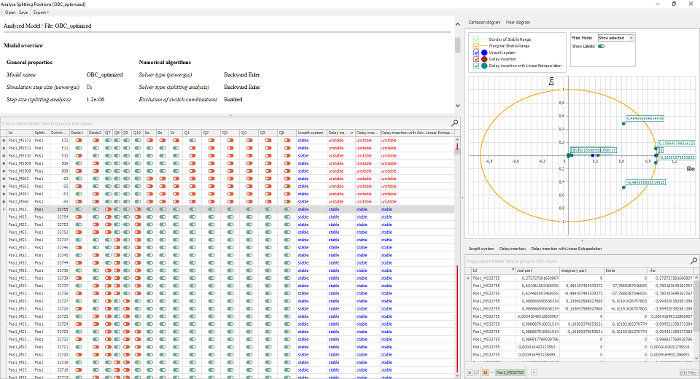

Les résultats de l’analyse sont clairement affichés graphiquement en cliquant sur le bouton « Generate stability results ». Outre les informations indiquant si la méthode de fractionnement respective, qui peut être sélectionnée via le bloc INTERFACE, assure un système global stable, instable ou légèrement stable pour la position de fractionnement examinée, les valeurs propres de la matrice système associée (étendue) sont également affichées. Tous les résultats peuvent être facilement filtrés et organisés comme souhaité.

Dans le présent modèle, on peut conclure de cette analyse que le modèle se comporte de manière stable même après insertion du bloc INTERFACE pour le fractionnement de modèle à condition qu'aucun court-circuit ne se produise dans le convertisseur DC/DC.

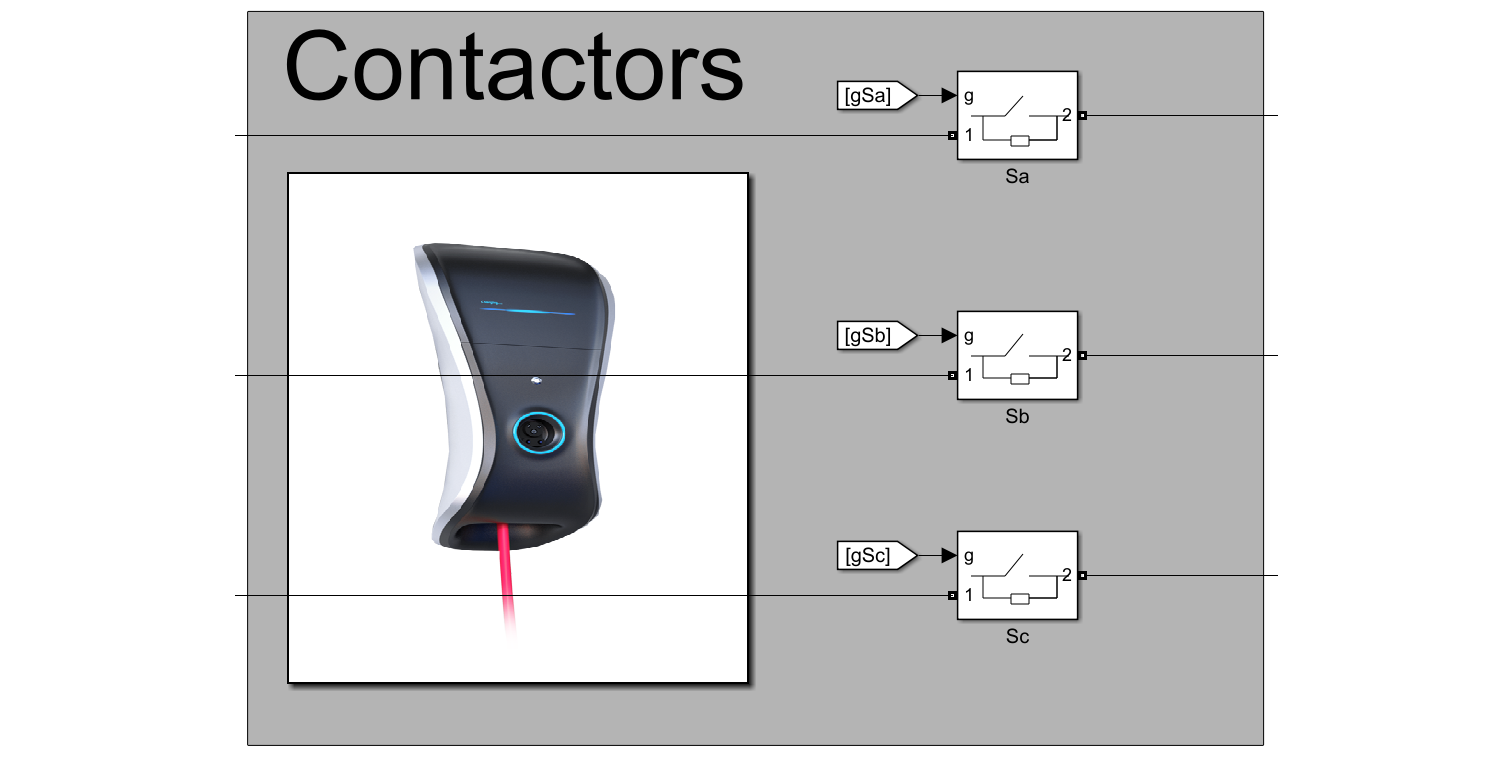

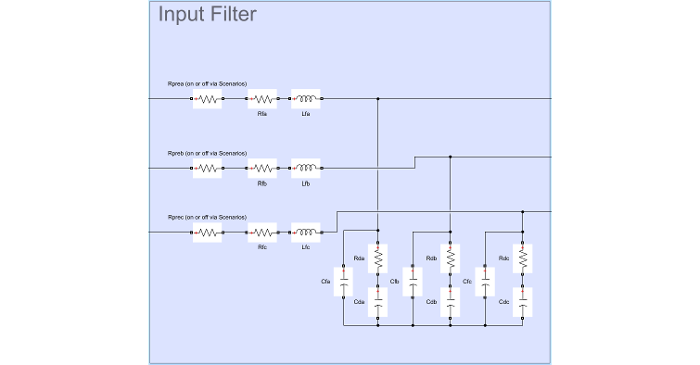

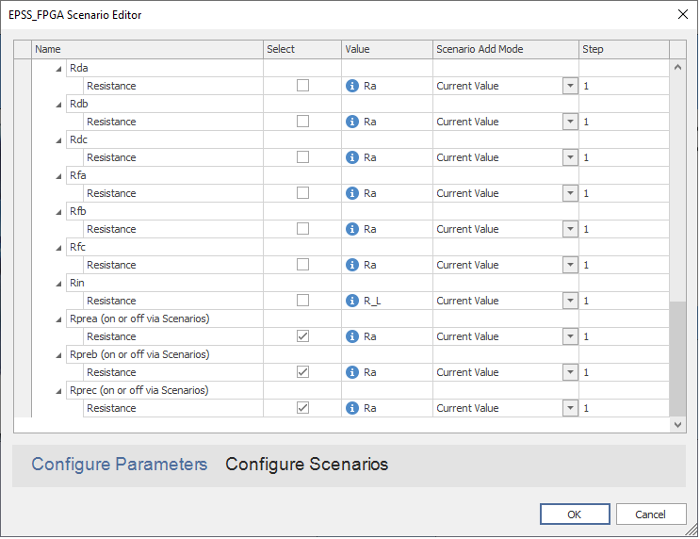

Réduction du nombre de commutateurs en tenant compte des configurations spéciales

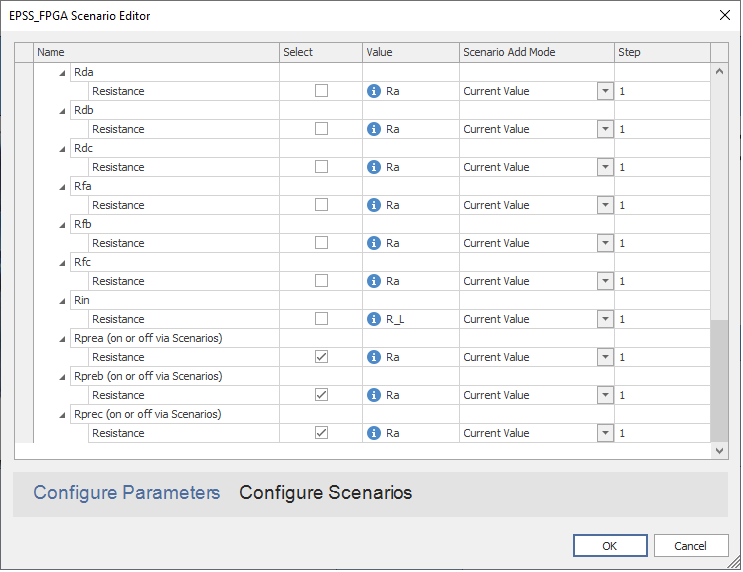

Il existe d'autres options pour réduire le nombre de jeux de matrices dans l'application temps réel en plus du fractionnement du modèle. Tout d’abord, les configurations de commutateurs spéciales peuvent être modélisées plus précisément. Dans le présent modèle, cela concerne les commutateurs Sa, Sb et Sc, qui commutent toujours simultanément. Il en va de même pour les commutateurs Rprea, Rpreb et Rprec dans le filtre. Ces commutateurs peuvent être facilement configurés en tant que commutateur triphasé à l'aide de la fonction ‘Exclude Switch Combinations’ fournie dans le pack EPSS (Electrical Power Systems Simulation) de dSPACE (en utilisant la même interface utilisateur graphique que pour l'analyse de fractionnement, configurable dans le bloc SETUP). Ils peuvent également être modélisés en tant que résistances et commutés pendant l’exécution à l'aide de la fonction « Scenarios » de l'EPSS. Nous utilisons ici une combinaison de fonctionnalités, c’est-à-dire que Sa, Sb et Sc sont modélisés en tant que commutateurs triphasés et que Sprea, Spreb et Sprec sont configurés à l’aide de scénarios.

Signal de démarrage pour la simulation temps réel

Après ces configurations, la fonction d'analyse ANALYZE_MODEL peut maintenant être réutilisée pour vérifier la capacité temps réel du modèle pour le FPGA disponible. Il s'avère qu'un fichier EPSS peut maintenant être généré pour le modèle, ce qui permet de l'exécuter sur le système temps réel avec une conception FPGA générique préconfigurée incluse dans le pack EPSS (Electrical Power Systems Simulation) de dSPACE (sans avoir besoin de synthèse).

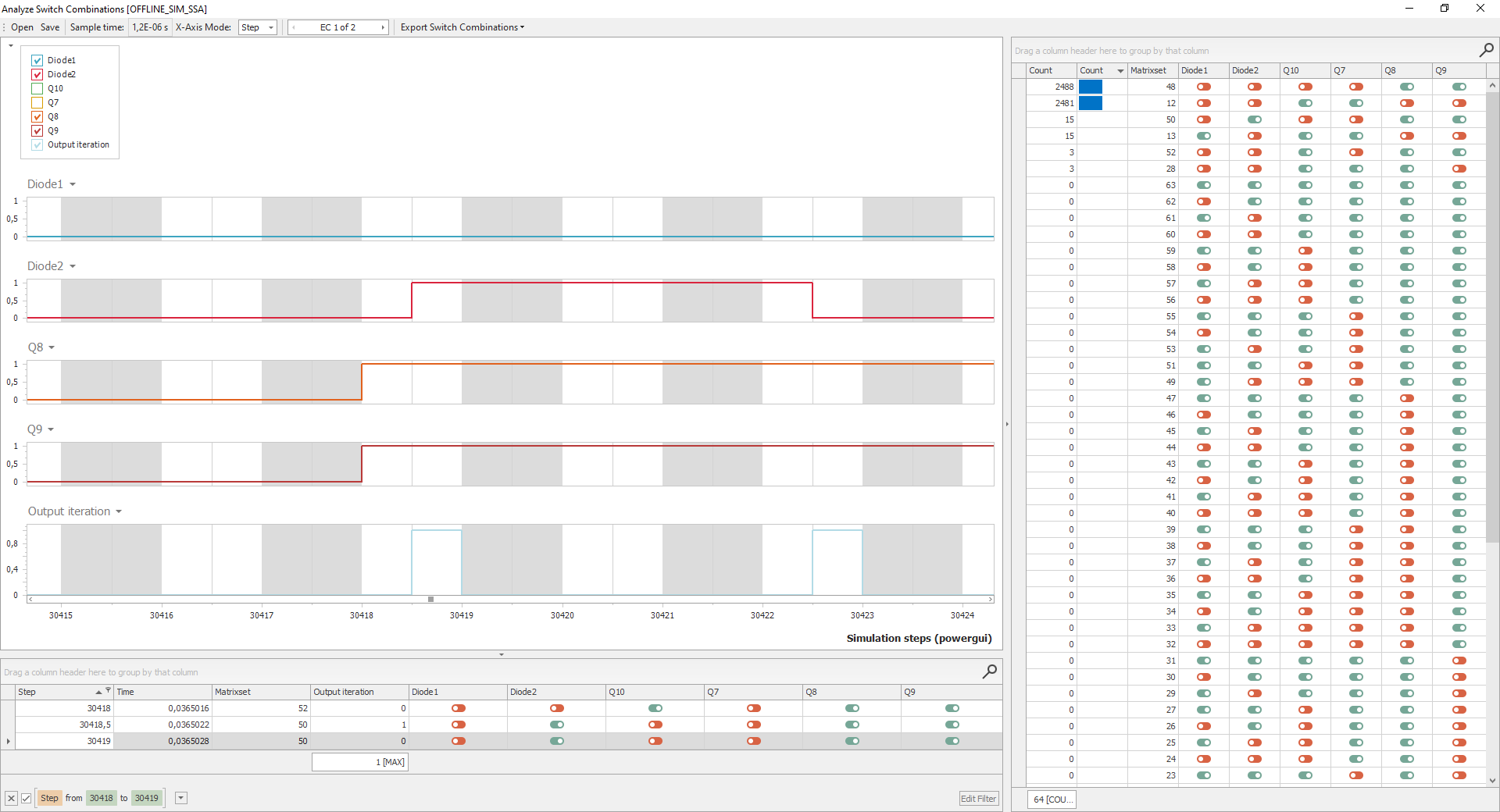

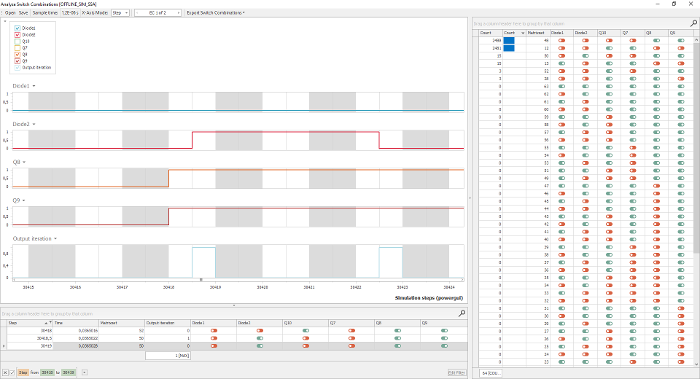

Étude hors ligne du comportement de commutation

La fonction « Analyze Switch Combinations » du pack EPSS (Electrical Power Systems Simulation) de dSPACE vous permet d'analyser les effets sur les éléments passifs du modèle de simulation pour un contrôle donné des commutateurs actifs. En utilisant le bloc OFFLINE_SIMULATION fourni dans l’EPSS, qui permet une simulation hors ligne du circuit au moyen de fonctionnalités spéciales fournies dans l’EPSS, tous les états de commutateurs survenant pendant la simulation peuvent être enregistrés et affichés sous forme graphique. Dans l’illustration suivante, vous pouvez notamment voir que lorsque la porte des appareils Q8 et Q9 (respectivement les blocs IBGT/diode) est activée, la diode2 ne s’allume pas avant l’étape de post-itération en réponse. Les zones grises et blanches représentent toujours une étape de simulation, les subdivisions au sein de ces zones symbolisent un ensemble d’étapes post-itération possibles. Dans la partie droite de l’image, vous pouvez également obtenir un aperçu de la fréquence à laquelle l’état de commutation est utilisé pour le contrôle du modèle considéré.

Informations complémentaires

- A. Kiffe, K. Witting, and F. Puschmann, "Systematic separation of electrical power systems for hardware-in-the-loop simulation," 2017 19th European Conference on Power Electronics and Applications (EPE'17 ECCE Europe), 2017, pp. P.1-P.10, doi: 10.23919/EPE17ECCEEurope.2017.8098995.

- A. Kiffe, K. Witting, and F. Puschmann, "Separation of Power Electrical Circuits for Different Computation Platforms," 2018 20th European Conference on Power Electronics and Applications (EPE'18 ECCE Europe), 2018, pp. P.1-P.10.

À propos de l'auteur

Katrin Witting

Directrice, Solutions de développement et test en temps réel, dSPACE GmbH