FPGA Programming Blockset

Integrating FPGA models in dSPACE systems

The FPGA Programming Blockset is a Simulink® blockset for using a FPGA model created with a dSPACE system using the Xilinx® Vitis™ Model Composer HDL Library, the former Xilinx System Generator Blockset.

-

FPGA Programming Blockset 2023-A – New Features

Support of MathWorks® HDL CoderTM for modeling parts of the FPGA model with Simulink® blocks

- Easy connection of FPGA models to processor models (Simulink®, ConfigurationDesk)

- Model-based I/O configuration

- Offline simulation in Simulink

Application Areas

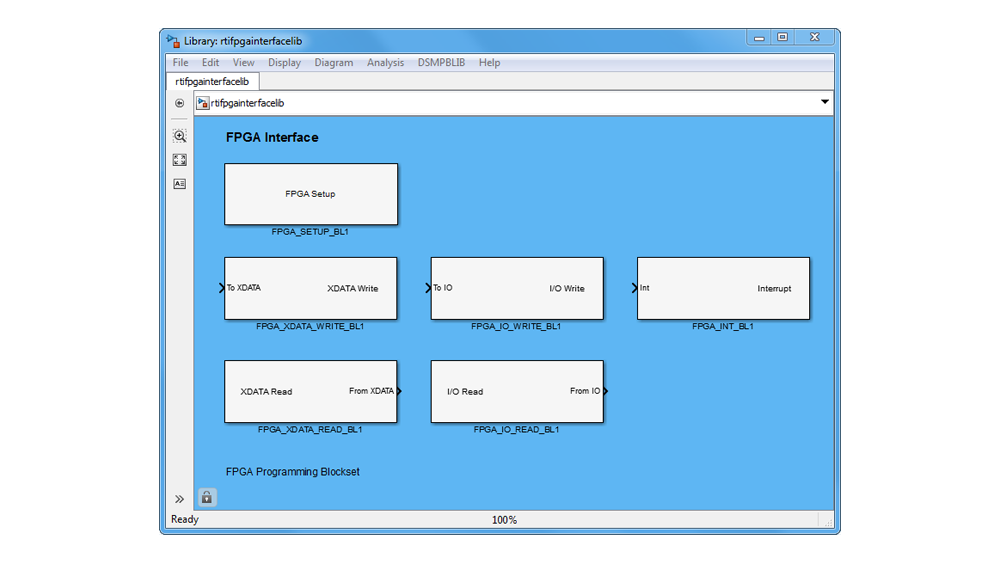

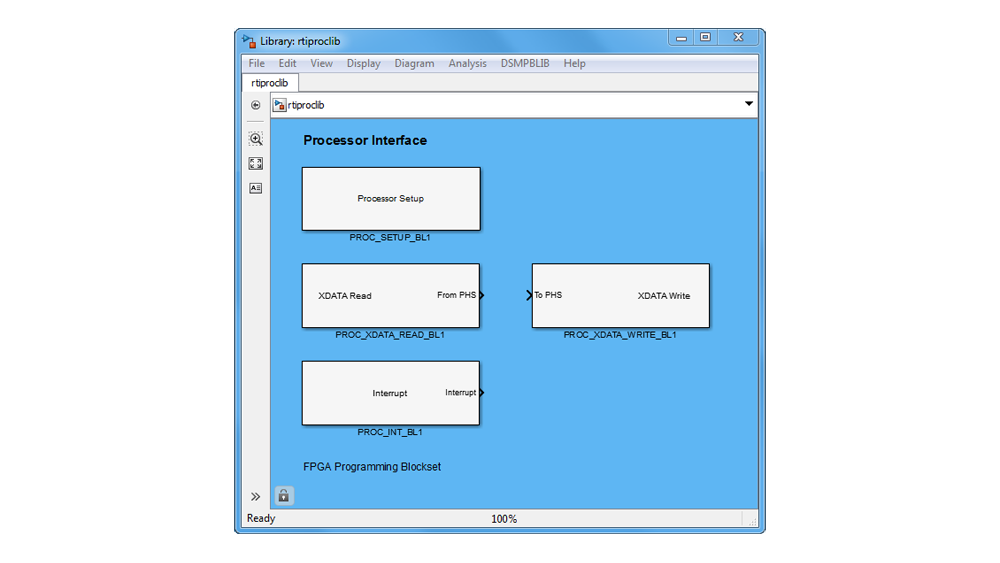

The FPGA Programming Blockset is a Simulink blockset for using a FPGA model created with a dSPACE system using the Xilinx® Vitis™ Model Composer HDL Library, the former Xilinx System Generator Blockset. It provides blocks for implementing the interface between the FPGA mounted on a dSPACE board and its I/O, and the interface between the dSPACE FPGA board and its computation node (CN).

The blockset can be used with the following dSPACE FPGA platforms, which provide user-programmable FPGAs:

- DS2655 FPGA Base Board and its I/O modules

- DS6601/DS6602 FPGA Base Boards and their I/O modules

- MicroAutoBox II 1401/1511/1514 and 1401/1513/1514 extended with I/O modules

- MicroAutoBox III 1403/1511/1514 and 1403/1513/1514 extended with I/O modules

- MicroLabBox

Typical application scenarios for rapid control prototyping (RCP) and hardware-in-the-loop (HIL) simulation are:

- Projects in the automotives, industrial automation, medical engineering, and aerospace industries

- Signal preprocessing, adapting new interfaces, very fast control loops, designing and testing new concepts for electrified powertrains

Key Benefits

The dSPACE FPGA platforms provide various cutting-edge Xilinx® FPGAs which can be programmed graphically with Xilinx Vitis™ Model Composer HDL Library in Simulink®.

The FPGA Programming Blockset lets you integrate the resulting FPGA design into a real-time application that runs on dSPACE hardware.

The blockset also gives you a convenient way to connect the I/O board’s I/O driver components and to model the connection to a processor-based computation node (SCALEXIO processing hardware, MicroLabBox, or MicroAutoBox). The data exchange supports fixed-point data types as well as floating-point data types.

To grant maximum freedom in developing FPGA applications, it is also possible to handcode the entire design using the handcode interface in VHSIC hardware description language (VHDL or Verilog). Alternatively, you can integrate handwritten IP cores into your Simulink FPGA model, or you can also use MathWorks® HDL CoderTM to model parts of the FPGA design.

With the FPGA blockset, you can synthesize, build, and program an FPGA or processor directly from Simulink for optimal convenience. During run time, you can access variables to trace or modify them, without having to modify the model. An FPGA scope even allows for an in-depth analysis of your design.

| Optional Hardware | Boards and Variants |

|---|---|

| SCALEXIO |

|

| MicroAutoBox |

|

| MicroLabBox |

|

| Functionality | Description |

|---|---|

| General |

|

| FPGA interface |

|

| Handcode interface |

|

| I/O access |

|

| Processor-FPGA communication |

|

| Inter-FPGA communication between SCALEXIO FPGA base boards |

|

| Asynchronous tasks |

|

| Variable access |

|

| Remote FPGA build |

|

| Support of MathWorks® HDL CoderTM |

|

Drive innovation forward. Always on the pulse of technology development.

Subscribe to our expert knowledge. Learn from our successful project examples. Keep up to date on simulation and validation. Subscribe to/manage dSPACE direct and aerospace & defense now.